Hardware Curriculum Designs

Hardware Curriculum Designs

硬件技术课程设计要求

- 教学目标

- 使学生能够对计算机硬件技术某个方面有深入的研究

- 具有一定的计算机硬件设计或应用能力

- 具有计算机底层软硬件技术相结合的编程开发能力

- 课程设计内容

基于Logisim完成MIPS单周期CPU的硬件设计

掌握基于MARS MIPS指令集的汇编语言设计

使用插入排序算法进行测试联调

一、 设计题目

单周期八指令MIPS CPU仿真搭建以及测试

二、 设计目的

使用logisim完成单周期八指令MIPS CPU仿真设计。

复习回顾计算机组成原理的课程内容。

培养计算机硬件设计或应用能力。

学习了解汇编语言及其使用。

使用汇编语言完成单周期八指令MIPS CPU测试。

三、 设计原理

1. 定长指令周期

本实验采用了定长指令周期,所有指令均在一个时钟周期内完成,即CPI=1。在实际应用中往往不会采用采用这种方案,原因是其效率低下,整体性能取决于最慢的指令,导致时钟周期过长。

与定长指令周期相对应的是变长指令周期,变长指令周期不受到最慢指令的限制。除此之外,变长指令周期还有多个优点:支持复用期间和数据通路;支持流水操作等。

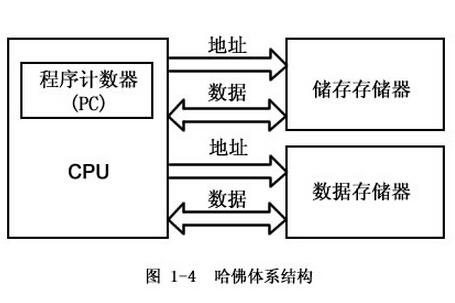

2. 哈佛结构

本实验采用的是哈佛结构,并非课本上曾经学习过的冯·诺依曼结构。哈佛结构是一种存储器结构,是一种并行体系结构,它的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问。哈佛结构示意图如图 三.2.1所示。

图 三.2.1, 哈佛结构示意图

3. 核心指令集

本实验计划设计8指令的单周期MIPS CPU,通过查阅《MIPS32指令手册》,整理得MIPS CPU,核心指令集及描述,如表 三.3.1所示。imm表示立即数。

| 序号 | MIPS指令 | RTL功能描述 |

|---|---|---|

| 1 | ADD rd, rs, rt | rd ← rs + rt |

| 2 | SLT rd, rs, rt | rd ← rs < rt 小于置1,否则置0 |

| 3 | ADDI rt, rs, imm | rt ← rs + imm |

| 4 | LW rt, offset(base) | rt ← memory[base + offset] |

| 5 | SW rt, offest(base) | memory[base+offset] ← rt |

| 6 | BEQ rs, rt, offset | if (rs = rt) then branch |

| 7 | BNE rs, rt, offset | if (rs ≠ rt) then branch |

| 8 | syscall | 系统调用, 这里用于停机 |

表 三.3.1, 本实验核心指令集

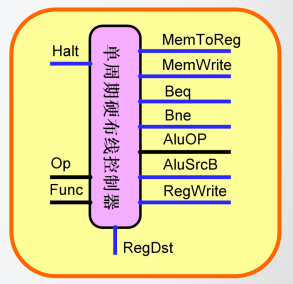

4. 单周期MIPS控制器设计

设计该实验首先要了解控制器的输入输出信号,进而规划数据通路,单周期MIPS控制器输入输出信号如图 三.4.1所示。

图 三.4.1, 单周期MIPS控制器输入输出信号图

输入信号:

指令字Opcode,Func字段。

输出信号:

| 序号 | 控制信号 | 信号说明 | 产生条件 |

|---|---|---|---|

| 1 | MemToReg | 写入寄存器的数据来自存储器 | LW指令 |

| 2 | MemWrite | 写内存控制信号 | SW指令 |

| 3 | Beq | BEQ指令译码信号 | BEQ指令 |

| 4 | Bne | BNE指令译码信号 | BNE指令 |

| 5 | AluOP | 运算器操作控制符 | 加法,比较两种运算 |

| 6 | AluSrcB | 运算器第二输入选择 | LW指令, SW指令, ADDI指令 |

| 7 | RegWrite | 寄存器写使能控制信号 | 寄存器写回信号 |

| 8 | RegDst | 写入寄存器选择控制信号 | R型指令 |

| 9 | Halt | 停机信号,取反后控制PC使能端 | syscall指令 |

表 三.4.1, 控制器输出信号及说明

四、 设计步骤

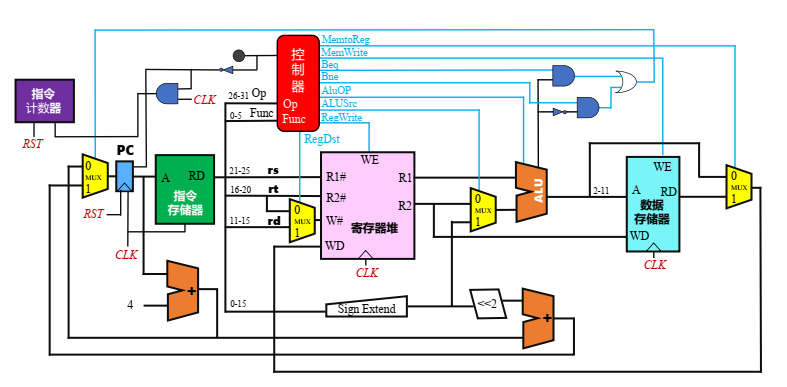

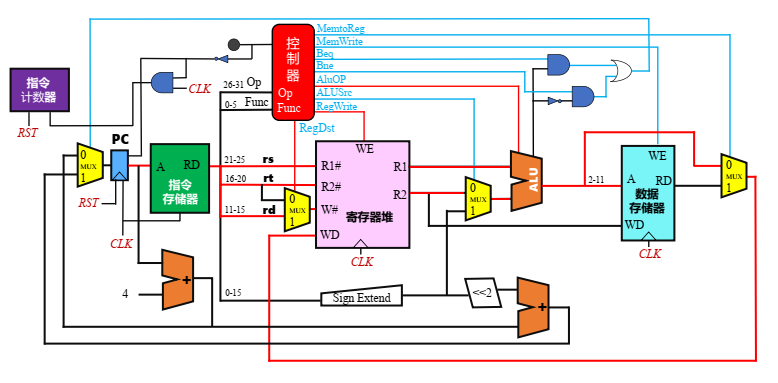

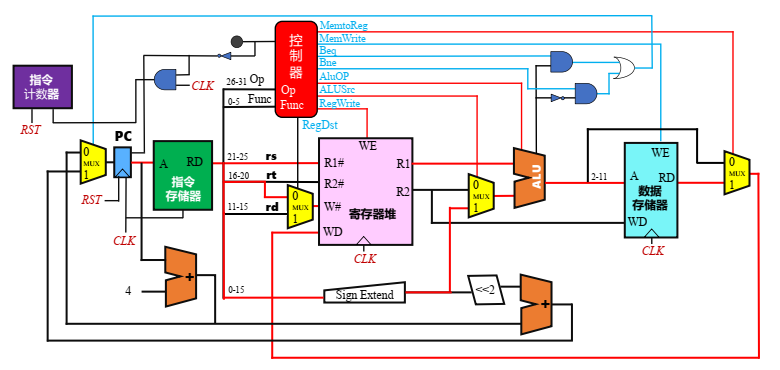

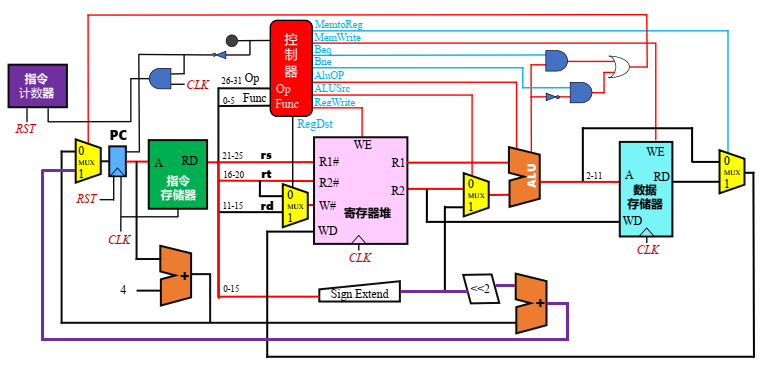

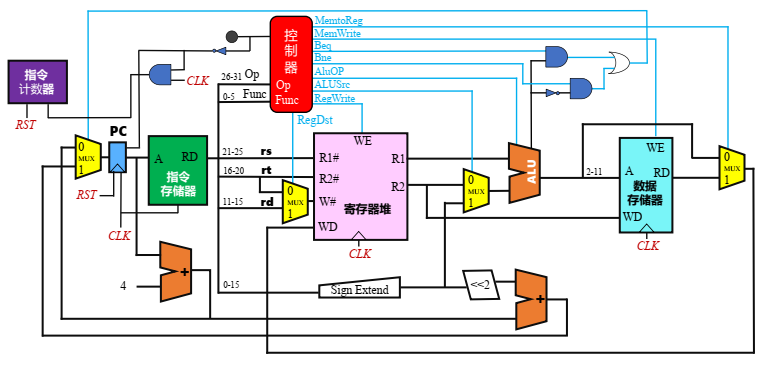

1. 单周期MIPS CPU数据通路和电路设计

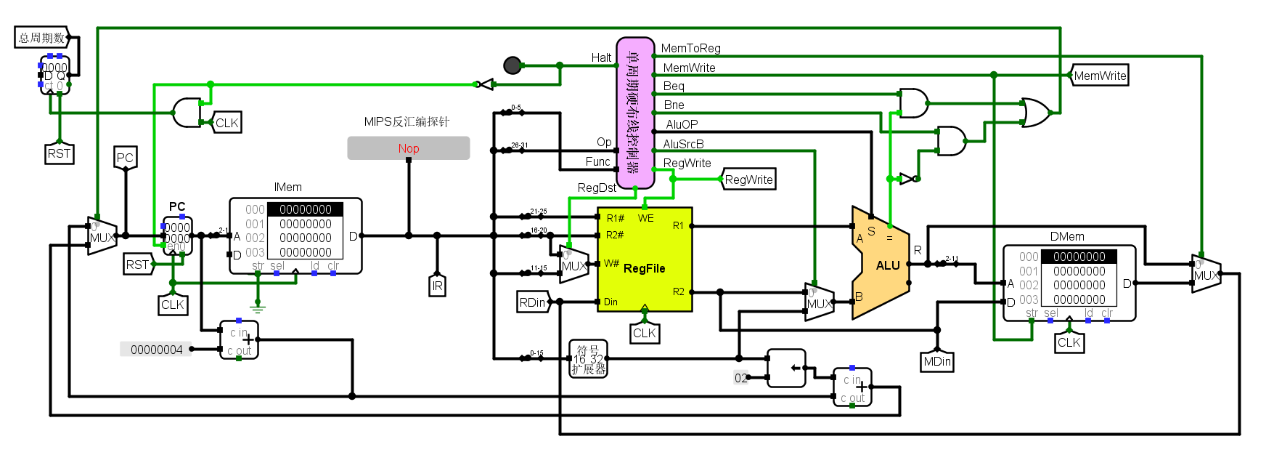

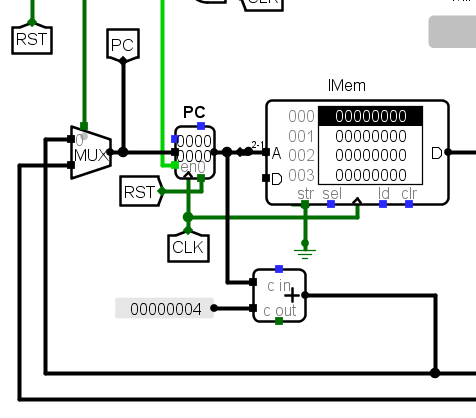

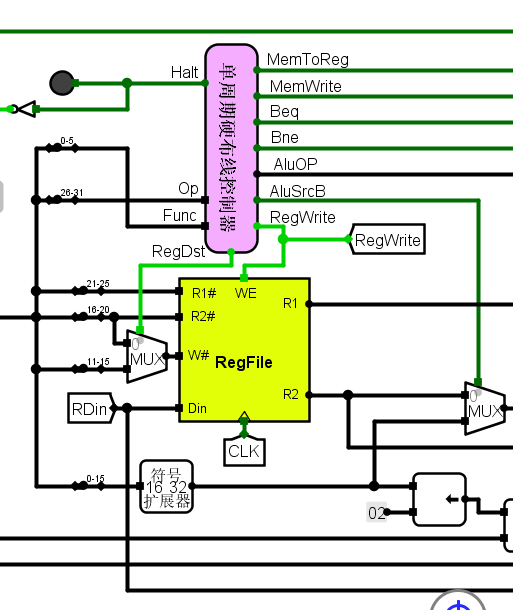

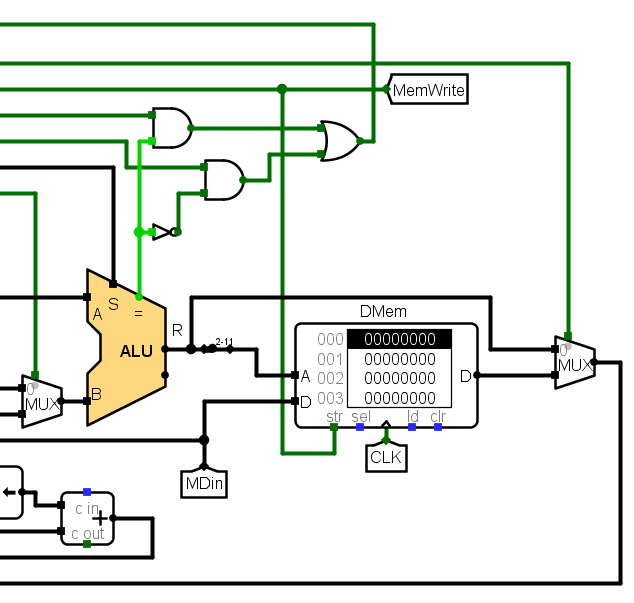

在给出组件的基础上,设计出数据通路和电路连线方式,总体数据通路图如图 四.1.1所示, R型指令数据通路图如图 四.1.2所示,LW指令数据通路图如图 四.1.3所示,SW指令数据通路图如图 四.1.4所示,Beq指令数据通路图如图 四.1.5所示,J型指令数据通路图如图 四.1.6所示。

图 四.1.1, 总体数据通路图

图 四.1.2, R型指令数据通路图

图 四.1.3, LW指令数据通路图

图 四.1.4, SW指令数据通路图

图 四.1.5, Beq指令数据通路图

图 四.1.6, J型指令数据通路图

2. 使用logisim软件进行连线绘制

连线方式按照此前的设计进行,logisim总体连线图结果如图 四.2.1所示, logisim指令寄存器(IMem)部分连线结果如图 四.2.2所示,logisim寄存器堆(RegFile)部分连线结果如图 四.2.3所示, logisim数据寄存器(DMem)部分连线结果如图 四.2.4所示。

图 四.2.1, logisim总体连线图

图 四.2.2, logisim指令寄存器(IMem)部分连线图

图 四.2.3, logisim寄存器堆(RegFile)部分连线图

图 四.2.4, logisim数据寄存器(DMem)部分连线图

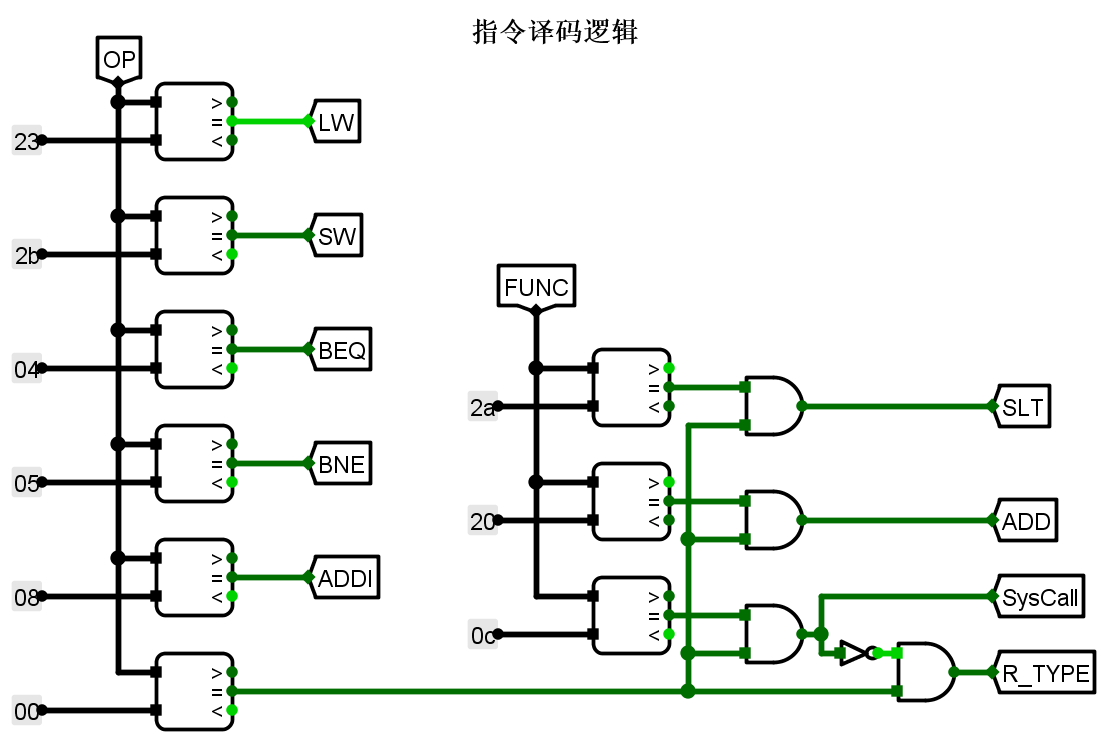

3. 设计绘制硬布线控制器内部逻辑电路

首先查阅《MIPS Green Sheet》,获得所需8个指令的Op和FUNC两个字段,结果如表 四.3.1所示。

| 序号 | 指令名称 | OPCODE(Hex) | FUNCT(Hex) |

|---|---|---|---|

| 1 | ADD | 0 | 20 |

| 2 | SLT | 0 | 2a |

| 3 | ADDI | 8 | - |

| 4 | LW | 23 | - |

| 5 | SW | 2b | - |

| 6 | BEQ | 4 | - |

| 7 | BNE | 5 | - |

| 8 | SysCall | 0 | c |

表 四.3.1, MIPS CPU指令字及对应的控制信号产生条件

LW,SW,BEQ,BNE,ADDI五个指令的译码逻辑较为简单,只需将OP信号与上表中的OPCODE进行比较即可。SLT,ADD,SysCall,R_TYPE四个指令则需要先与OP信号比较,再与FUNCT比较。其中SysCall和R_TYPE较为特殊,R_TYPE表示R型指令,SysCall是一种特殊的R型指令,不属于R_TYPE。二者之间的逻辑是若OP信号和FUNC信号满足SLT或ADD两个指令之一,R_TYPE逻辑成立,因为SLT和ADD均为R型指令,属于R_TYPE。而在OP信号和FUNC信号满足SysCall指令的OPCODE和FUNCT时,R_TYPE逻辑不成立,因为SysCall是一种特殊的R型指令,不属于R_TYPE。最终完成的电路图如图 四.3.1所示。

图 四.3.1, 指令译码逻辑电路图

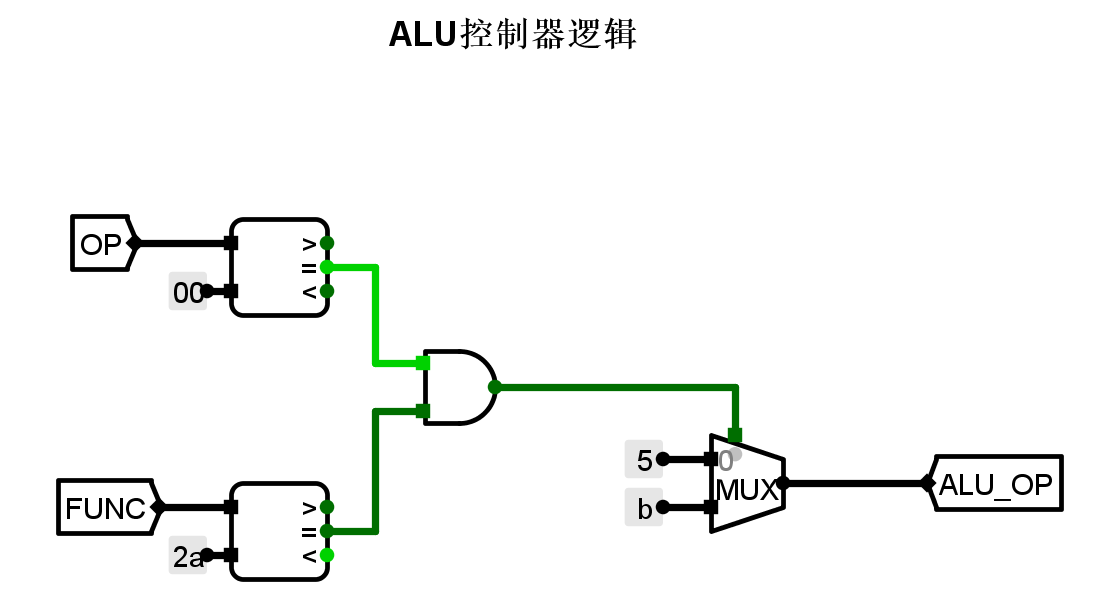

ALU控制器逻辑的设计方法与指令译码逻辑的设计方法类似,首先通过网络查找MIPS ALU 规格,结果如表 四.3.2所示。本实验的8条指令中只有ADD和SLT两条指令涉及到ALU_OP,即加法和比较。

| 序号 | 指令名称 | OPCODE(Hex) | FUNCT(Hex) | ALU_OP(Hex) |

|---|---|---|---|---|

| 1 | ADD | 0 | 20 | 5 |

| 2 | SLT | 0 | 2a | b |

表 四.3.2, MIPS CPU指令字及对应的ALU规格

由于本实验涉及到的指令只有两条,所以ALU控制器逻辑的设计较为简单。当OP信号和FUNC信号满足STL指令的OPCODE和FUNCT时与门输出1,使多路选择器输出的ALU_OP为b(Hex), 代表STL指令;否则输出5(Hex),代表指令ADD。最终完成的电路图如图 四.3.2所示。

图 四.3.2, ALU控制器逻辑电路图

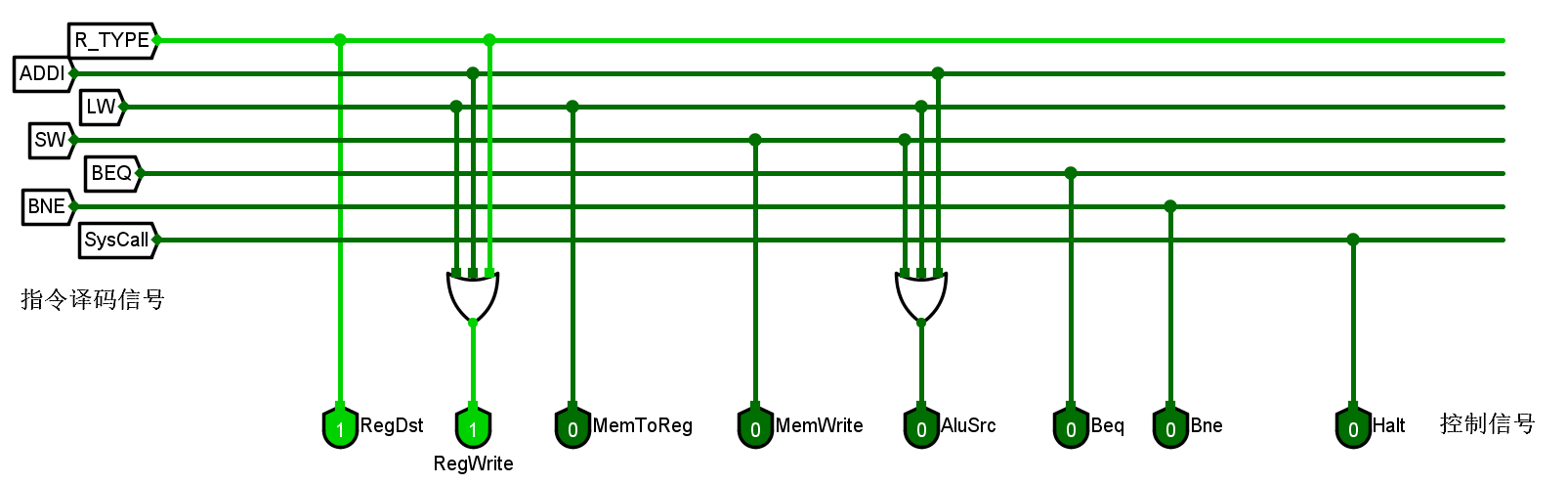

4. 设计绘制控制信号逻辑电路

根据表 三.4.1控制器输出信号及说明,进一步进行分析得到表 四.4.1。然后根据表格连接电路,最终完成的电路图如图 四.4.1所示。

| RegDst | RegWrite | MemToReg | MemWrite | AluSrc | Beq | Bne | Halt | |

|---|---|---|---|---|---|---|---|---|

| R_TYPE | 1 | 1 | ||||||

| ADDI | 1 | 1 | ||||||

| LW | 1 | 1 | 1 | |||||

| SW | 1 | 1 | ||||||

| BEQ | 1 | |||||||

| BNE | 1 | |||||||

| SysCall | 1 |

表 四.4.1, MIPS CPU控制信号产生条件

图 四.4.1, 控制信号逻辑电路

五、 实验结果

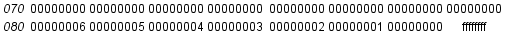

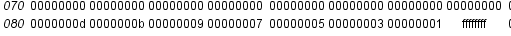

在设计出的单周期MIPS CPU上运行冒泡排序算法进行测试,首先执行sort.hex文件,对-1,0,1,2,3,4,5,6进行降序排序,排序结果会储存在数据寄存器的0x80位置上。结果如图 五.1所示。

图 五.1

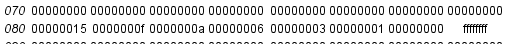

可以对汇编程序进行修改,将-1,0,1,2,3,4,5,6改成奇数数列-1,1,3,5,7,9,11($b_{hex}$),13($d_{hex}$),如图 五.2所示。

图 五.2

也可以随机设置一组数据进行排序,如图 五.3所示:

图 五.3

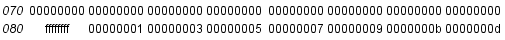

还可以修改程序,进行升序排序,这里采用了与图 五.2相同的奇数数列,如图 五.4所示:

图 五.4

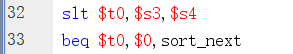

这里修改数据只需要在汇编程序的数据初始化部分修改数值即可,而修改降序排序为升序排序,需要将汇编程序33行的beq比较修改为bne比较即可实现。

图 五.5

如图 五.5所示,32行的含义为:如果$s3 > $s4,则$t0 = 1,否则$t0=1,33行的含义为:如果$t0 = $0则执行sort_next,$0为0。综合起来以高级编程语言表示即为:

1 | if ($s3 < $s4){ |

如果将beq改为bne即表示:如果$t0≠$0,则执行sort_next。综合起来以高级编程语言表示即为:

1 | if ($s3 >= $s4){ |

通过以上的推导,就实现了降序排序向升序排序的转化。

六、 实验中遇到的问题及解决方法

在本次实验中,我遇到了许多的问题,在解决这些问题的过程中收获了许多知识和技能。

1. 设计绘制电路

通过在网络上查找资料,我找到了一些相关的博客、文档。按照上面介绍的方式和截图完成连线以后我发现许多地方电路出现了不必要的复杂,在一些细节上不同博客和文档甚至是完全相反的。于是我反复观看了MOOC上的课程,复习了曾经学习过的《计算机组成原理》,结合课程设计指导给出的数据通路图,成功将电路进行简化,并且解决了资料中矛盾的地方,并顺利完成测试。

2. 设计绘制控制器内部逻辑电路和ALU控制逻辑电路

这一部分的内容课本上没有查阅到,网络上的资料也只是给出了结果,并没有详细的解释。于是我根据结果查阅课程设计提供的《MIPS Green Sheet》和《MIPS32指令手册》两份文件,找到了Op和FUNC两个信号的意义、8条指令的对应的Op和FUNC信号值,并对结果进行整理分析,得到了表 四.3.1,表 四.3.2,表 四.4.1三个表格。明白了原理以后,再看网络资料上给出的结果,发现ALU控制器逻辑电路冗杂的使用了两个比较器,我将电路进行修改,使用一个与门和一个比较器就完成了电路的逻辑设计。

3. 汇编语言和汇编程序

由于此前我没有学习过汇编语言,在一开始进行测试的时候只能简单的导入程序然后运行,无法自己修改程序。我通过在网络上查找资料和视频进行了学习,熟练掌握了所涉及到的8条MIPS指令。通过学习,我现在已经可以修改程序和排序的数据,进行降序/升序排序的转换。最终对不同的程序进行了测试,均成功实现计划的功能。

七、 设计总结

通过这次硬件技术课程设计,我复习巩固了计算机组成原理的课程内容,并且对CPU的设计,MIPS指令,汇编语言有了更加深入的理解。在计算机组成原理理论课程和本课程设计对应的MOOC上已经对理论知识有了一定的了解,这使得我在完成本设计时思路较为清晰。除此之外,老师和同学们在课程上的讨论和讲解也对我完成课程设计并且深入理解起到了很大的作用。

这次课程对于我来说更重要的收获是总结归纳出了适合自己的解决问题的方法论。在遇到问题时,首先要对问题的基础知识有大致的了解。然后通过互联网搜索相关资源,如Github,许多个人博客等,这些资源能给我很大的指导和帮助,起到事倍功半的效果。但同时要对这些资源保持怀疑,带着批判的角度去学习这些资料,认真检查和理解,并且进行自己的测试。在本次课程设计中,我就在这一步发现了许多互联网资源的错误和冗余。深入理解这些资料的同时,如果遇到问题,及时查询解决。这样问题导向式的学习更加高效,快捷,理解也会更加深刻。下一步对资料中错误和冗余的部分进行修改,并尝试进行简化。最后在现有资源的基础上进行拓展和创新,比如我在本次课程设计中对冒泡排序的算法进行修改,可以实现排序数字、升序\降序的随意切换。我将这样的过程总结成“站在巨人的肩膀上”的过程。首先需要大致了解问题,明确爬上巨人的肩膀具体是要做什么的;其次查找资料,找到巨人;再次带着批判的角度理解资料,即从巨人的脚下爬上肩膀,并且检查巨人本身是否有问题;然后改正发现的问题,删除冗余,即确保巨人是站得稳的;最后在已有的基础上进行拓展和创新,即站在巨人的肩膀上,向更高的地方探索,让自己成为“巨人肩膀上的巨人”。